MDIO接口(Management Data Input/Output Interface),最早在IEEE 802.3的第22卷定义,后来在第45卷又定义了增强版本的MDIO,其主要被应用于以太网的MAC和PHY层之间,用于MAC层器件通过读写寄存器来实现对PHY层器件的操作与管理。

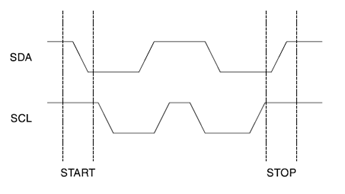

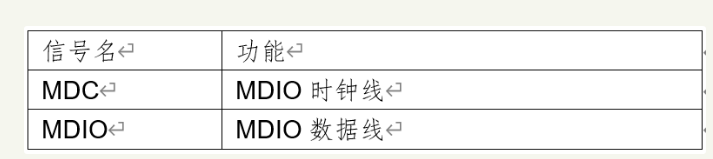

MDIO接口包括两条线,MDIO和MDC,其中MDIO是双向数据线,而MDC是由STA驱动的时钟线。

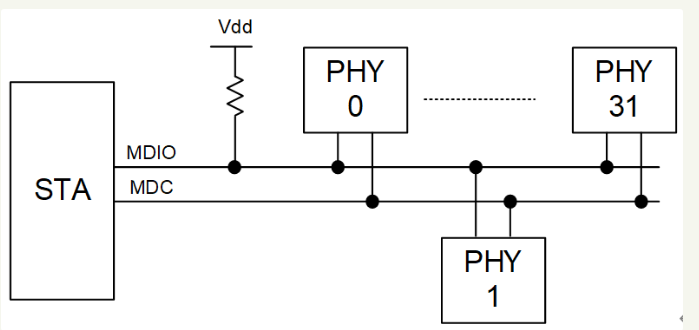

STA(Station Management)为主控设备,比如MCU、MAC、ONU等。PHY为从设备。一个STA最多管理32个PHY。MDC信号由STA控制,MDIO信号根据通信方式的不同可以由STA或者PHY接管控制。通常MDIO会通过电阻上拉至接口电源。

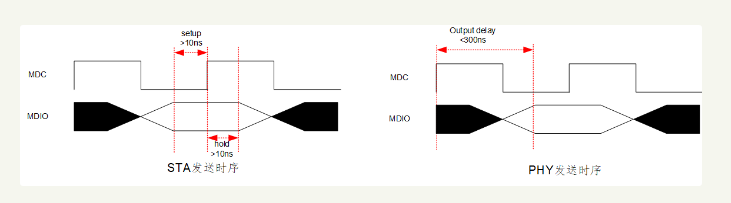

MDC为MDIO接口时钟信号,来自STA,用来对MDIO的数据采样。MDC可以是非周期性信号。协议对MDC的高低电平的最大宽度并没有限制,仅限制了MDC的最小高低电平宽度不能小于160ns,最小周期不能小于400ns。这意味着MDC最高频率不能超过2.5MHz。

MDIO为MDIO接口数据信号,为双向信号,STA和PHY均可以接管。用来在PHY控制芯片和PHY芯片之间的传递控制和状态信息。MDIO接口只是会在MDC时钟的上升沿进行采样,而并不在意MDC时钟的频率(类似于I2C接口)。当MDIO由STA输出时,需要满足建立时间、保持时间均大于10ns。当MDIO由PHY输出时,需要满足输出延迟不超过300ns。

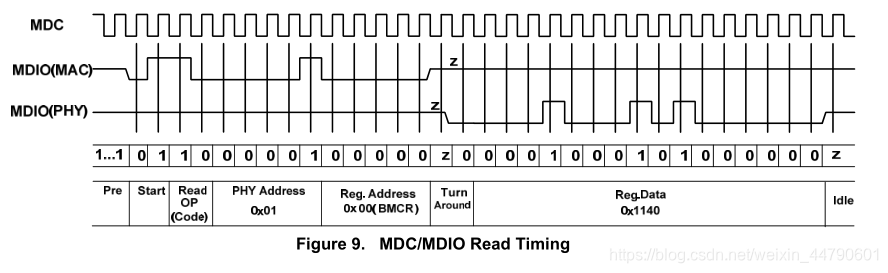

读时序

通过MAC发送PHY Address(芯片地址)及Reg Address(芯片上寄存器的地址)来驱动PHY芯片,读取PHY芯片的这个指定地址上的值(即Reg Data部分),然后释放总线。

Pre:信号头 共发送1*32bit

Start:开始 01

OP Code:操作码 读为10

PHY Add:物理地址 共5bit

Reg Add:寄存器地址 共5bit

TA:翻转缓冲 第一位为Z,第二位收到回读的0

Reg Data:回读来自寄存器的数据 回读期间MAC输出保持Z,收到来自寄存器的16bit数据

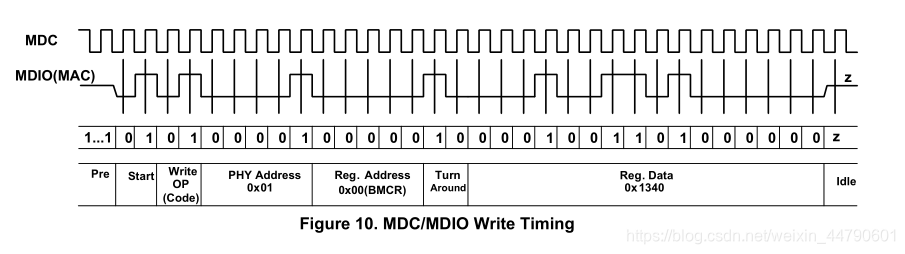

写时序

在MAC直接发送总线上的数据(Reg Data),到指定的外部芯片地址PHY Address 中的指定寄存器(Reg Address)中。

Pre:信号头 共发送1*32bit

Start:开始 01

OP Code:操作码 写为01

PHY Add:物理地址 共5bit

Reg Add:寄存器地址 共5bit

TA:翻转缓冲 发送10

Reg Data:回读来自寄存器的数据 回读期间MAC输出保持Z,收到来自寄存器的16bit数据