测试的目的就是为了验证生产出来的芯片是否达到当初的设计要求(spec需求),通过测试对芯片进行筛选分类,把一些残次品分选出来;把好的产品推向市场,不好的留着做后续的分析处理,以便改进设计或加工工艺,从而提高整个芯片的良率。

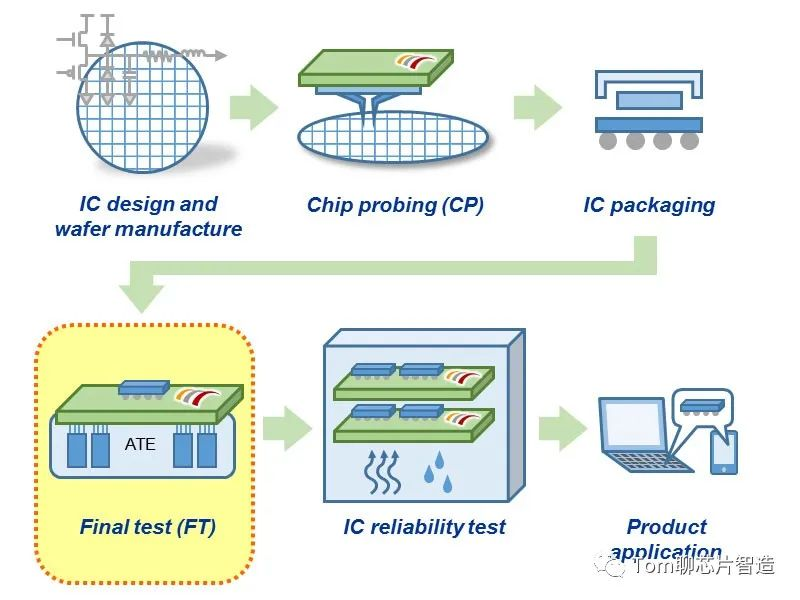

测试流程

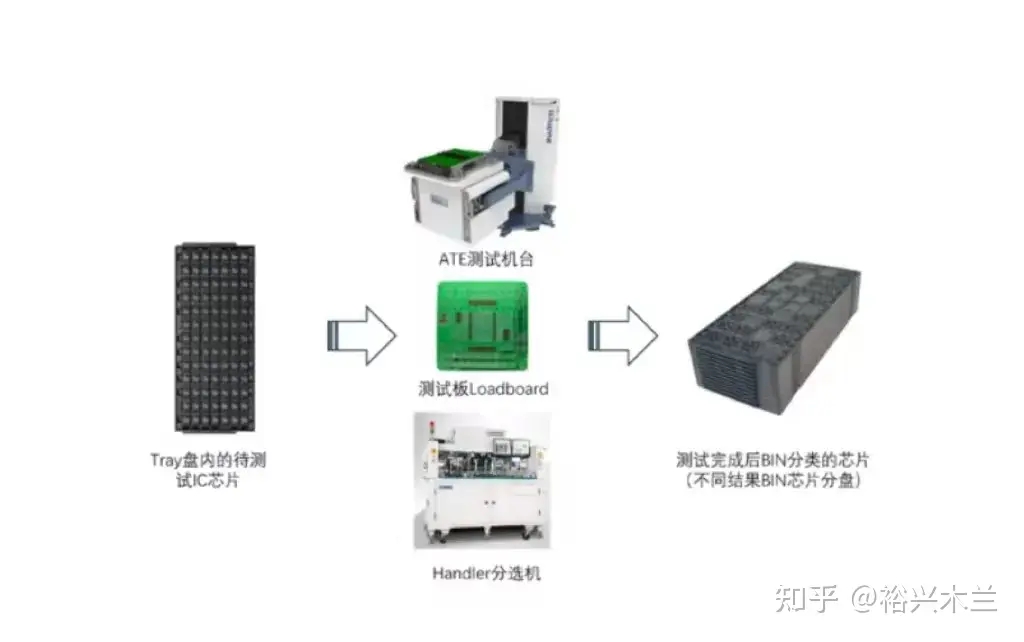

整个芯片的生产流程如下图,在整个生产中,需要对芯片进行两次测试,一是Wafer测试(Wafer Probe),二是Final 测试(Final Test);

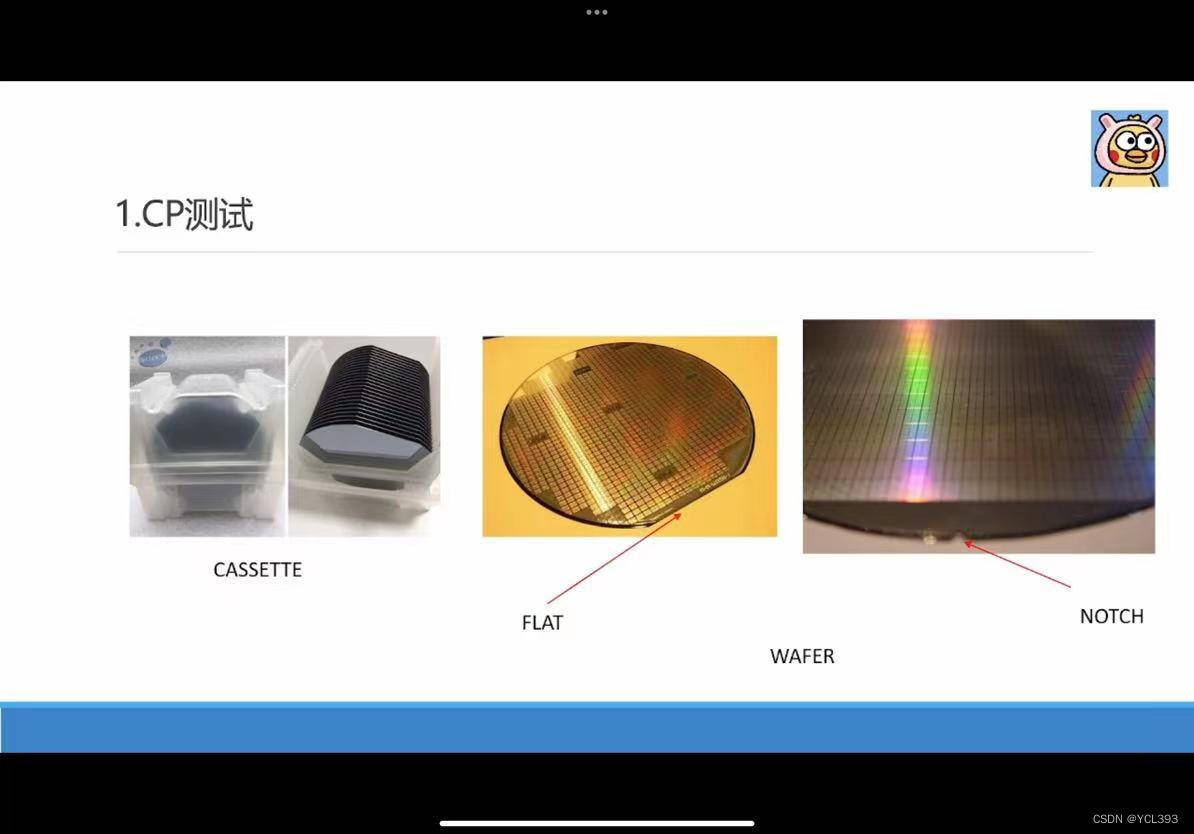

CP测试(Chip Probing)

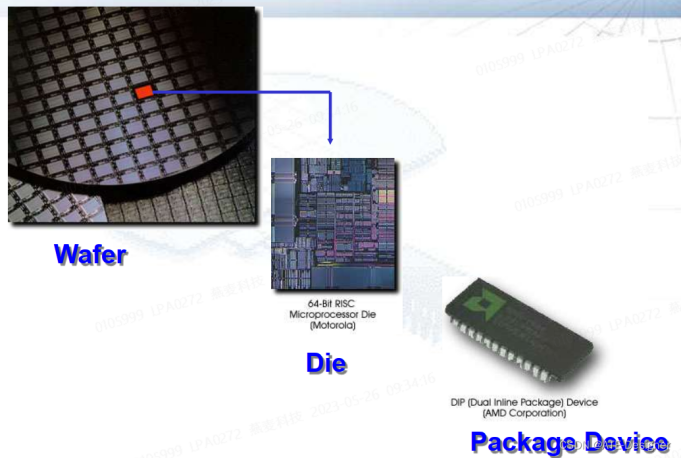

Wafer测试是使用探针台(Prober)+测试机(ATE)对Wafer上每个Die进行测试(每个Die最终会封装成一颗芯片,如下图所示),并把测试的结果标记出来,以便后续进行处理。

FT测试(Final Test)

Final 测试也叫封装测试,这个阶段是在芯片封装完后进行最终的测试,使用的机器是测试机(ATE)+ 分选机(Handler),通过测试的芯片会根据测试的结果对其进行分类,也就是分BIN处理。

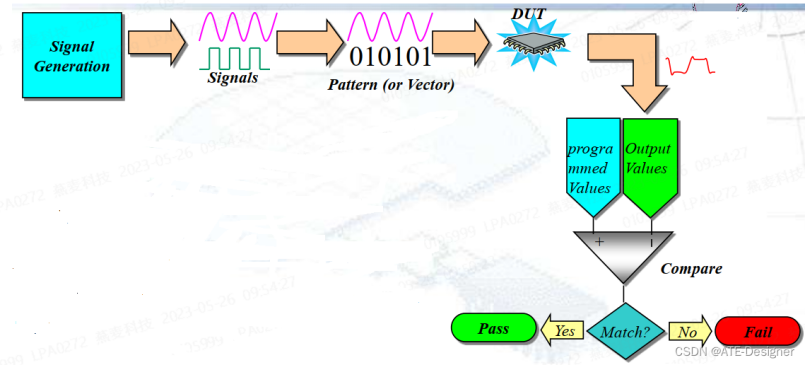

总的来说,芯片测试就是使用ATE产生一些信号(stimulus)输入给待测芯片(DUT),监测DUT的输出(或反馈)的结果,然后把结果和标准值(希望值或者设计值)进行比较,看是否达到要求,如下图所示:

测试项目

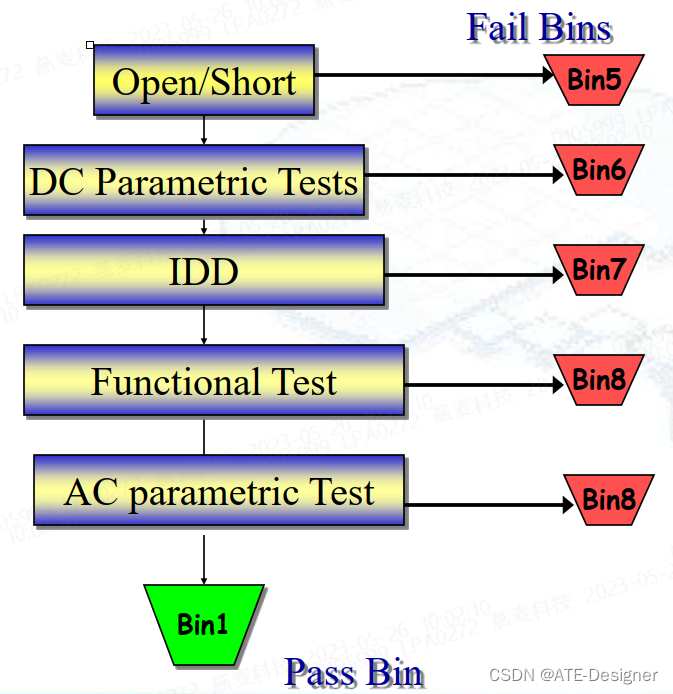

芯片测试的内容主要包含OS测试(Open/Short)、DC测试、IDD测试、Functional测试和AC测试,典型的流程如下图所示,这些内容将会在后续的章节进行详细介绍。

Open/Short Test: 检查芯片引脚中是否有开路或短路;

DC TEST: 验证器件直流电流和电压参数;

IDD:动态电流测试;

Function TEST: 测试芯片的逻辑功能;

AC Test: 验证交流规格,包括交流输出信号的质量和信号时序参数;

OS/CON测试

OpenShort指开短路测试,简称OS。CON即Contact,指接触测试。

此项测试主要检测芯片引脚是否存在开/短路现象,各输入输出引脚内部的ESD二极管是否正常工作,同时验证IC与socket之间是否形成良好的欧姆接触。不存在开/短路且阻值符合要求的为良品芯片。

测试内容

引脚结构的阻值。

测试本质

二极管压降

测试条件

芯片不供电,加流测压

IC开短路测试(open_short_test)又叫continuity test 或contact test,它是一种非常快速发现芯片的各个引脚间的是否有短路,及在芯片封装时是否missing bond wires.通常都会被放测试程序的最前面.它还能发现测试时接触是否良好,探针卡或测试座是否有问题.

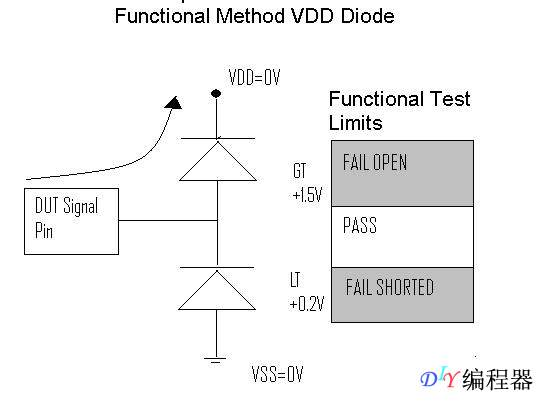

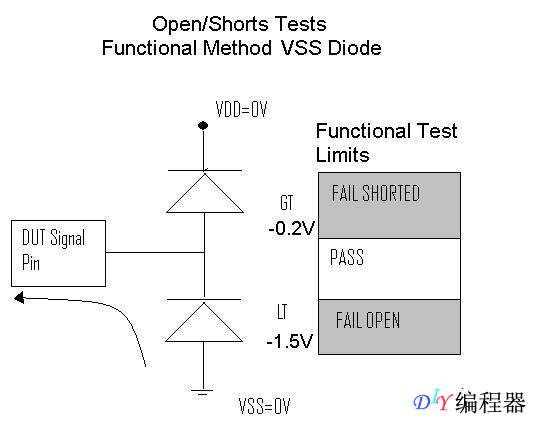

开短路测试的测试原理比较简单,分open_short_to_VDD 测试和open_short_to_VSS测试.一般来说芯片的每个引角都有泄放或说保护电路,芯片内部保护电路。是两个首尾相接的二极管,一端接VDD,一端接VSS。

信号是从两个二极管的接点进来.测试时,

1.先把芯片的VDD引脚接0V(或接地)

2. 再给每个芯片引脚供给一个100uA到500uA从测试机到芯片的电流,电流会经上端二极管流向VDD(0V)

3. 然后测引脚的电压,正常的值应该是一个二极管的偏差电压0.7伏左右,我们一般设上限为1.5伏,下限为0.2伏,大于1.5伏判断为openfail,小于0.2伏判断为shortfail。这就是open_short_to_VDD测试。

open_short_to_VSS测试的原理基本相同.同样把先VDD接0伏,然后从芯片中抽取一个小电流(uA~mA级别),电流由VSS经下端二级管流向测试机,然后测引脚的电压。同样正常的值应该是一个二极管的偏差电压-0.7伏左右,上限还是为-0.2伏,下限为-1.5伏,小于-1.5伏判断为openfail,大于-0.2伏判断为shortfail.这就是open_short_to_VSS测试.

所以对测试机里的测试器件来说,只要能给电流测电压的器件都能做开短路测试,只是精度有差异,效率有高低。

如果要判断其他所有引脚之间是否存在短路,可以在测试某一引脚时将其他全部引脚接0V,继续按照OS测试的方法测试。如果发生短路则该Pin也会被短路到近似0V。也可以使用测试机的并行测试,但此时并行测试的引脚之间发生的短路将无法被检测到。

如果器件引脚不存在ESD二极管,则一般无法使用此方法进行OS测试。

DC测试

芯片测试中的直流(DC)特性测试是指通过测量芯片的直流电特性参数(例如电流、电压、电阻)来验证芯片电学性能是否符合设计要求的过程。

直流测试是IC测试的基础,是检测电路性能和可靠性的基本判别手段。测试时主要考虑测试准确度和测试效率。通过直流测试可以判明电路的质量。如通过接触测试判别IC引脚的开路/短路情况、通过漏电测试可以从某方面反映电路的工艺质量、通过转换电平测试验证电路的驱动能力和抗噪声能力。

一、电源电压测试

电源电压测试主要测量芯片在不同电压下的电流变化,旨在确定芯片的最小和最大电源电压范围。测试人员会向芯片的电源端口输入不同的电压,然后测量芯片的电流变化,以获取芯片的最小和最大电源电压。

二、地引脚测试

地引脚测试主要是为了测量芯片的接地电压,以确定该接地电压是否符合设计规范。如果接地电压不合规范,可能会导致芯片失效或其他问题。

三、I-V测试

I-V测试是一种重要的电学测试,用于测量芯片中电流和电压之间的关系。这个过程需要在恒定电压下,测量芯片中的电流变化,或在恒定电流下测量芯片中的电压变化。这可以使测试人员确定芯片在不同电压或电流下的性能,以验证生产线上或客户端的使用中的性能是否在应用范围内。

四、电阻测试

电阻测试用于测量芯片中不同部件之间的电阻大小,并确保其在设计要求的合理范围内,避免可能导致芯片失效或产生其他问题的电阻问题。

六、漏电流测试

七、转换电平测试

八、输出电平测试

九、电源消耗测试

芯片测试中的直流特性测试对于验证芯片电学性能的关键特性至关重要,可以提高芯片的可靠性和性能,确保其正常工作。

常见测试项

输入PAD:VIL/VIH,IIL/IIH

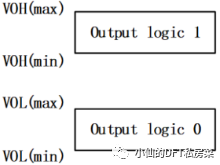

输出 PAD:VOL/VOH,IOL/IOH

双向PAD:VIL/VIH,IIL/IIH,VOL/VOH,IOL/IOH

三态输出PAD:VOL/VOH,IOL/IOH,IOL/IOH

测试方法

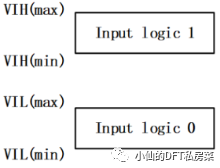

1 VIL/VIH(加流测压,FIMV)

1.1 测试目的

测试芯片输入IO能正确识别输入电压VIL/VIH,测试DC参数在设计范围内。

VIL,表示输入管脚正确识别logic0时的最大电压参数;

VIH,表示输入管脚正确识别logic1时的最大电压参数。

1.2 测试方法

在规定的测试温度下,芯片放入测试平台,将所有IO置为输入状态,分别在VDDmax/VDDmin mode下验证VIL/VIH。

2 VOL/VOH(加流测压,FIMV)

2.1 测试目的

测试芯片在一定的负载情况下,芯片IO输出高低电平在规定的范围内。

VOH,表示管脚输出高电平时的最低电压;

VOL,表示管脚输出低电平时的最高电压。

2.2 测试方法

在规定的测试温度下,芯片放入测试平台,将所有IO置为输出状态,在VDDmin mode下验证VOL/VOH。

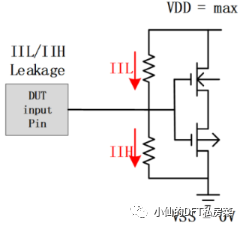

3 IIL/IIH(加压测流,FVMI)

3.1 测试目的

IIL,测试时给IO施加低电平,可以测出VDD到IO的测量输入管脚的漏电流,测算出阻抗是否在设计范围内;

IIH,测试时给IO施加高电平,可以测出IO的测量输入管脚到VSS的漏电流,测算出阻抗是否在设计范围内。

3.2 测试方法

在规定的测试温度下,芯片放入测试平台,将所有IO置为输入状态,在VDDmax mode下测试漏电流。

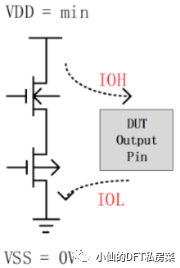

4 IOL/IOH(加压测流,FVMI)

4.1 测试目的

IOL,测量IO输出低电平时的电流大小,通过测量电流可以间接测量到IO内阻的大小;

IOH,测量IO输出高电平时的电流大小,通过测量电流可以间接测量到IO内阻的大小。

4.2 测试方法

规定的测试温度下,芯片放入测试平台,将所有IO置为输出状态,在VDDmin mode下测试漏电流。

5.Iq/Idd测试

静态电流Iq是指芯片在空闲状态时,消耗的最大电流

目的:挑选出功耗较大的IC

静态电流较大的IC一般意味着器件存在结构缺陷,或者已经损坏,有时也会在测试完功能后再测试静态电流,如一些闪灯芯片

测试方法:一般是对IC的VDD脚加电压,其它脚悬空,测试IC消耗的电流

其它情况可能有要求对IC的所有输入脚置高或低电平再测试静态电流,可根据资料要求来测试

动态电流Idd是指芯片在工作状态时,无负载时消耗的最大电流

目的:挑选出功耗较大的电路

因为IDD较大的IC一般意味着器件存在结构缺陷,或者已经损坏。

测试方法:一般是对IC的VDD脚加电压,给IC的工作条件,使IC进入工作状态

※对同一颗IC施加同样的电压,静态电流一定比动态电流小

静态电流和动态电流测试,相当于是测试IC的VDD与GND之间的阻抗,

如VDD=5V,IQ上限为5uA, 根据欧姆定律得到可接受的最小阻抗为1M欧姆

当为静态时阻抗较大因而测到的电流较小,为动态时阻抗较小,测得的电流较大

AC测试

交流参数测试测量器件晶体管转换状态时的时序关系,是以时间为单位验证与时间相关的参数,实际上是对电路工作时的时间关系进行测量,测试的目的是保证器件在正确的时间发生状态转换。输入端输入指定的输入在特定时间后在输出端检测预期的状态转换。

常见的AC测量参数有上升和下降时间、传输延迟、建立和保持时间、存储时间、频率等。交流参数最关注的是最大测试速率和重复性能,然后为准确度。此处只对频率测试进行介绍。

频率测试通常测试芯片指定管脚的输出频率,常见的有振荡端,测试端,COM脚,SEG脚,PWM输出频率测试

测试目的:

①、器件在规定的参数条件下,是否可正常起振

②、器件在规定的参数条件下,输出频率是否符合设计或应用要求。

可靠性测试

可靠性测试对于芯片的制造和设计过程至关重要。通过进行全面而严格的可靠性测试,可以提前发现并解决潜在的设计缺陷、制造问题或环境敏感性,从而确保芯片在长期使用中的性能和可靠性。

这种测试旨在验证芯片在不同环境条件下的稳定性、可靠性和持久性,以确保其能够长时间稳定地运行。可靠性测试包括多种测试项目,例如温度测试、电压测试、功能测试和可靠性持久性测试。

1.温度循环测试

芯片温度循环测试的测试目的是评估芯片在不同温度条件下的性能和可靠性,以模拟实际使用环境中的温度变化。该测试旨在验证芯片在温度变化时是否能够正常工作,以及是否能够保持稳定性和可靠性。温度循环测试通常涵盖了芯片所需的操作温度范围,包括常温、极端高温和低温。具体温度范围根据芯片的设计要求和应用场景来确定。测试中会进行多个温度循环,其中一个循环包括一段时间的高温暴露和一段时间的低温暴露。循环次数可以根据芯片的设计寿命要求来确定。

在高温循环期间,芯片被暴露在高温环境中,可能是通过热板、热箱来实现。高温环境下的测试可以揭示芯片在高温条件下的性能特性,例如功耗变化、时钟频率的稳定性、信号完整性等。这有助于验证芯片在高温环境下的可靠性,并识别潜在的热问题。

在低温循环期间,芯片被暴露在低温环境中。低温测试可以揭示芯片在低温条件下的工作能力,例如冷启动性能、低温下的功耗和时钟稳定性等。此外,低温测试还可以检测芯片材料和封装的可靠性,以确保其在极端低温环境下的耐用性。

2.高温存储测试

高温环境可能引发以下问题:

功耗变化:长时间高温存储可能导致芯片内部电路中的漏电流增加,从而增加功耗。

参数漂移:芯片内部的电气特性参数可能会随着温度的变化而发生漂移,导致性能降低。

可靠性问题:高温存储可能导致芯片内部材料的老化和退化,可能导致可靠性问题,如电路断路、电子迁移等。

高温存储测试的原理是模拟芯片在长时间存储期间可能面临的高温环境,以评估芯片在这种条件下的性能和可靠性。这种测试有助于发现潜在的可靠性问题,预测芯片在实际使用中可能遇到的问题,并采取必要的措施来改善芯片设计、材料选择或封装技术。

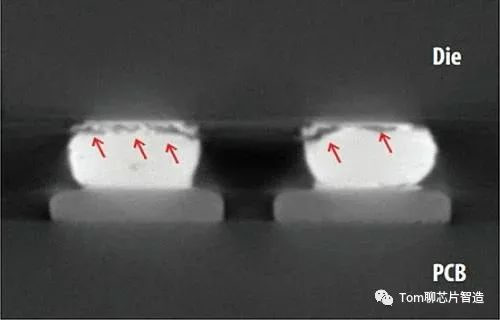

3.跌落测试

芯片跌落测试的主要目的包括:

评估芯片在跌落或冲击情况下的机械强度和可靠性。检测芯片封装材料和焊接的可靠性。验证芯片内部结构和连接的稳定性,以防止内部部件松动或脱落。评估芯片在实际使用中受到物理冲击时的性能损坏情况。

通过进行跌落测试,确定其在实际使用中是否能够承受跌落或冲击,并保持正常功能和结构完整性。这种测试有助于发现潜在的机械弱点、封装问题或连接失效。

4.加速应力测试(uhast)

芯片的uHAST测试是通过施加极端的电压和温度条件来加速芯片在短时间内的老化和故障模式。具体的uHAST测试条件,包括高温、高湿、压力和偏压值,以下是一些常见的uHAST测试条件的参考数值:

高温:通常在大约100°C至150°C的温度范围内进行,具体温度取决于芯片的设计要求和应用环境。有时候,更高的温度也可能被用于特殊情况下的测试。

高湿度:一般的uHAST测试中,相对湿度通常保持在85%至95%之间。高湿度条件下会加剧芯片的老化和腐蚀。

压力:测试期间施加的压力可以通过测试装置或封装环境来实现。压力的具体数值通常在2大气压(atm)至20大气压之间,具体数值取决于测试要求和芯片的应用场景。

偏压:偏压通常指施加在芯片引脚或器件上的电压。具体的偏压数值取决于芯片的设计和应用需求。在uHAST测试中,偏压可以用于加速故障模式的产生,例如漏电流、击穿等。

以上只是常见的几种可靠性测试方法。其他还有电磁干扰 测试,电压波动测试,电气特性测试,长时间运行测试等。

分立器件测试参数

二极管

正向导通电压UF

将二极管负极接地,正极接测试机电源端口,FIMV,施加规定的正向导通电流IF,测量对应电压。

反向工作电压UR

反向工作电流IR

三极管

MOS管

源漏击穿电压BVDSS

MOS漏源击穿电压。将MOS的栅极与源极接地(关断),漏源间施加特定电流(一般为250uA,取决于芯片参数),测量此时的电压。

在FT测试中,给定测试规范中的电压值,测量电流,若低于250uA则MOS尚未击穿,即PASS。

漏源饱和电流IDSS

MOS截止状态下的漏源泄漏电流。将MOS的栅极与源极短路接地(关断),在MOS的漏极源极之间加一个特定电压UDS(通常为略低于BVDSS的值)测量此时的漏电流。

漏源饱和电流IDSS

导通电阻RDSON

MOS在导通状态的漏源间电阻值。在MOS的栅极源极之间加一个大于Uth的电压(通常10V)使MOS开启,在漏极与源极间加一规定电流,测量此时的漏源电压,计算可得MOS的导通电阻。