本文最后更新于 310 天前,其中的信息可能已经有所发展或是发生改变。

简单来说,一组Bank就是共用一个电源的一组I/O管脚。

为了提高器件使用灵活性,便于管理和适应多种电器标准,FPGA器件的IO引脚被划分为若干个组(bank),连接到同一个外部电压下。每个bank的接口标准由其接口电压Vcco决定,一个bank包含多个Vcco引脚,这些引脚必须与相同的外部电压相连,即同一bank只能有一种Vcco,但不同bank的Vcco可以不同。Vcco电压相同是接口标准的基本条件,只有相同电气标准的端口才能连接在一起。

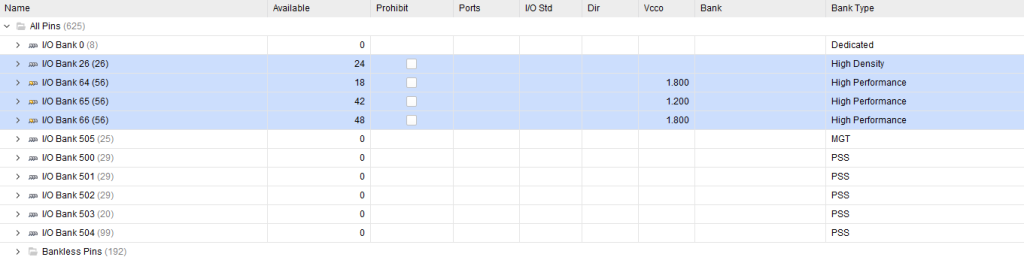

上图所示器件共有625个引脚,总共有11个bank,其中bank26,bank64,bank65,bank66是PL侧bank,其余的都是PS侧bank。

- bank0:一般用来作为ADC电压输入,温度传感器输入,以及部分配置端口;

- bank26 : HD bank;

- bank64,65,66 : HP bank;

- bank50x ; PS侧使用的bank;

在ultrascale器件中,会把PL侧bank分为HP,HD,HR三种,HP bank一般用来满足高速接口,电压最高支持到1.8V;HR bank一般用来满足高范围电平接口,电压最高支持到3.3V; HD bank用来支持低速接口;ultrascaler器件会组合使用HP,HD,HR bank,但是不保证在同一个器件中同时会有3个类型的bank。另外DCI接口只能使用在HP bank上。