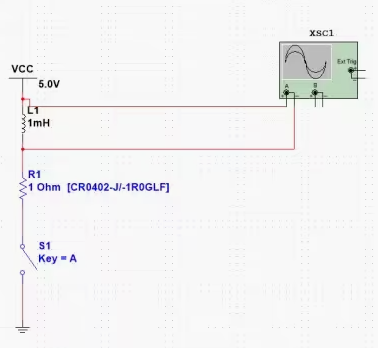

如下图所示的电路中,当开关从闭合转为断开时,由于电感电流不会突变,电压会发生骤升出现尖峰。这一尖峰电压可能导致把开关和其他电子元件击穿。

为消除尖峰,可以给电感并连一个电容,将多余的能量转移给电容充电。但是直接并联会组成RC并联产生谐振。

由于电感电容都是储能元件,假设刚开始是电感中有能量电容中无能量,那么电感就会向电容充电,充至能量全部耗尽时,电容再反过来给电感充电,循环往复,若都是理想元件无ESR(等效串联电阻),电压波形会像正弦波一样震荡下去。

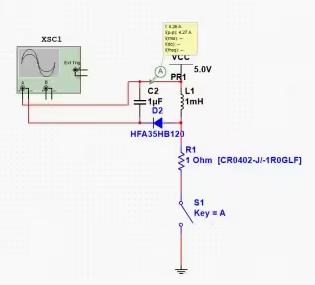

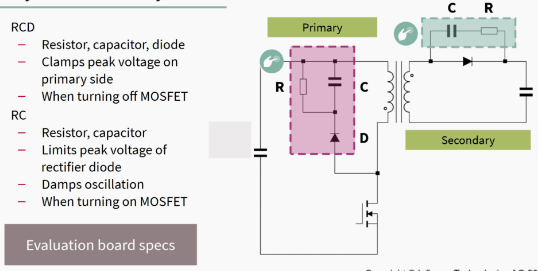

此处的设计只希望电感把能量转移给电容,这样的单向性容易想到二极管的单向导通,因此在电感与电容之间加入一个二极管。即构成一个由电阻R、电容C和二极管D组成的RCD吸收电路。

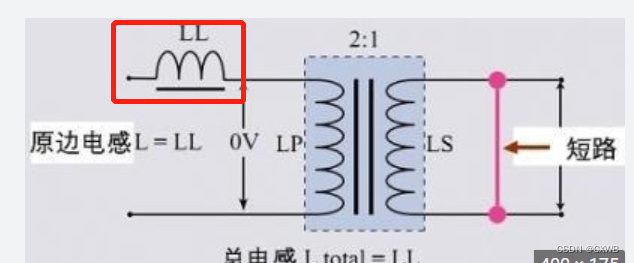

RCD电路主要应用在<反激电路>中。在反激电路中,变压器是非理想的,原边绕组中会存在无法耦合到副边的感量,称为漏感LL。可以将电路等效为一个理想原边电感串联一个漏感。

漏感值的测量方法为:短路输入绕组,测量原边的感量。由于输入绕组短路,磁芯磁路被短路,耦合到副边的能量都被短路了,还能测量出来的电感量便是漏感。

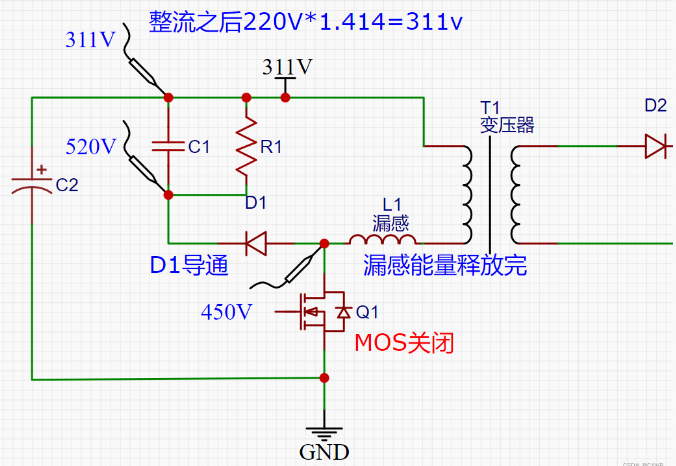

由于电感的电流不能突变,当开关mos管断开时,阻抗近似无穷大,漏感上的电流A会形成极高的瞬时电压,导致MOS管击穿损坏。因此会在原边电感并联RCD吸收电路,如下图所示。

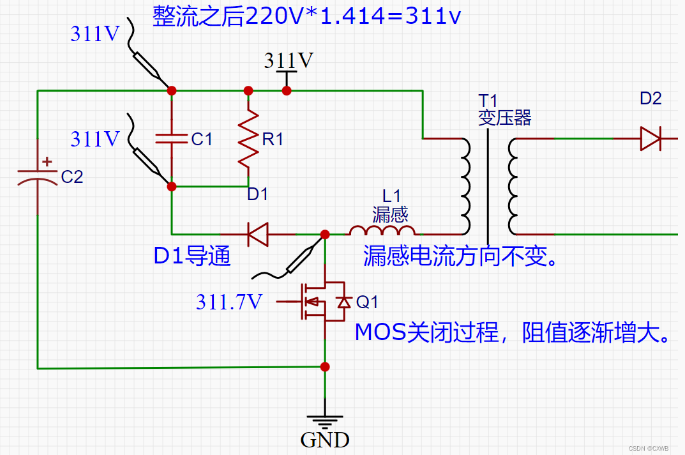

当MOS导通时,漏极接地,变压器原边两端形成压差,电流线性上升,同时漏感串联在电路内,电流也线性上升。

当MOS由导通变为关闭,变压器储存的能量转到副边,而漏感的能量无法转移到副边。漏感电流方向不变(从右到左),而MOS已经断开(可以看做阻值无限大)漏极的电压逐渐升高。当升高到311+0.7V,D1就会导通给C1充电。

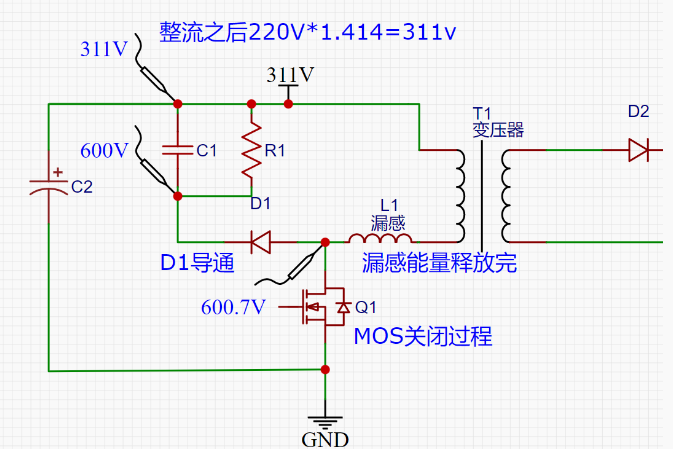

同时由于副边的反射电压,会在输入电压和反射电压叠加形成MOS的电压平台,漏感尖峰叠加在MOS平台电压之上。当MOS漏极电压比C1的下面的电压高0.7V时,二极管就会导通,漏感存储的电流流向C1,C1的电压逐渐升高,直到漏感能量完全释放完。

漏感能力释放完之后,MOS漏极的电压下降到平台电压,二极管截至。直到下一个周期MOS管导通再关闭的时候,漏感尖峰比C1电压高了才能重新导通。在重新导通之前,C1上面的电压会被R1消耗,逐渐下降。直到下一个周期漏感尖峰电压重新充电。如此反复。

- 漏感尖峰电压会被RCD吸收,漏感能量一定,电容越大,电容充电的电压就越低,吸收能力就越强,MOS漏极的电压就越低。

- 在漏感能力释放完之后(这个过程一般只有一个周期的3%时间),是要通过R1释放掉电容吸收的能量的,把电容的电压降下来方便下一次漏感尖峰来之前再进行吸收。

- 电容容量和电阻需要合理搭配,容量足够即可,足够能吸收漏感尖峰电压,不至于超过MOS耐压。电阻需要足够小,小到在放电阶段把电容电压下降到MOS的电压平台。但是不能下降到低于电压平台,否则就会把电压平台和母线电压之间的能量也吸收释放掉。

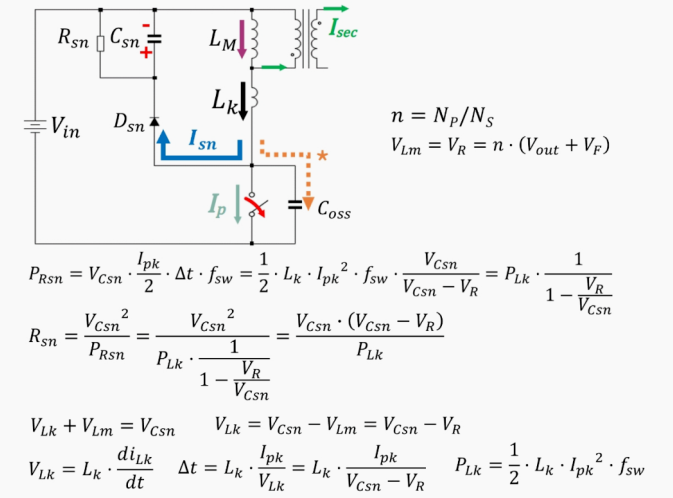

| 变量 | 公式 | 注释 |

| τ时间常数 | τ=RC | R在充电是电容ESR+PCB线抗+二极管阻抗,放电时是R1 ,C是C1 |

| 电容充电时的电压变化Uc | Uc=U×[1-e(-t/τ)] | Uc是电容电压,U是漏感在MOS漏极形成的电压,e=2.71828 |

| 电容放电时的电压变化Uc’ | Uc’=Uo×e(-t/τ) | Uo是放电前电容两端电压 |

| 漏感储能公式 | W=1/2LI² | |

| R1的功耗 | R1应该全部吸收掉漏感能量 |

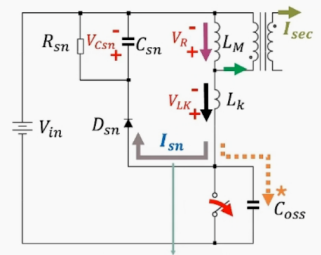

设计RCD缓冲电路时,预先设定缓冲电容器电压(Vcsn)和反射电压(VR),VR是次级输出绕组通过变压器匝比的反射电压。

当MOSFET关断时,Lk电流保持初始方向,忽略流向Coss的电流,假设全部电流流向Csn,相当于电感器与电压源串联,为电容器充电。

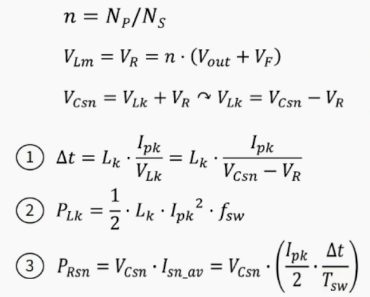

由公式1计算出漏感的放电时间t。由公式2算出Lk对Csn的充电功率Plk,进入电容器的电能要被电阻Rsn消耗,Prsn由公式3得到。

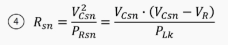

确定VCsn和Vr后,通过公式4计算Rsn的值,选择一个开关周期放电后的最小可接受Csn(Vl)值。VL应始终高于(Vin+Vr),VH为Vcsn的初始值。

Dsn选用快速二极管,注意二极管的耐压要大于等于MOSFET的耐压,1A的二极管可至少满足100W的反激。正常情况下, Trr为500nS的Dsn可满足数十瓦的反激功率。如果开关频率高,且散热条件差,应当使用超快速二极管,Trr要小于100nS。如选用慢管则只适用于小功率,建议小于10W。