ESD的危害和防护

ESD对器件造成损伤

大多数ESD损害发生在人的感觉范围以下。人对静电放电的感知电压是3KV,而很多电子元件在几百伏甚至几十伏就会损坏。

1)静电吸附灰尘,降低元件绝缘电阻,缩短寿命。

2)静电放电破坏,使元件受损(完全破坏)

3)静电使元件潜在损伤(半击穿)

4)热失效:多发生于双极型器件,PN结二极管、肖特基二极管等。

5)电过应力:熔化器件内金属

解决方法?

- 作业环境和包装

- 人员:静电手环;静电服

- 环境:离子风机、风枪;工具接地

- 包装:静电屏蔽袋

- 器件设计-ESD防护模块

- 透明性

正常状态下不工作,ESD脉冲出现时快速开启,结束后及时关闭。 - 有效性

低触发电压,低导通电阻,快速开启,钳位能力 - 鲁棒性

抵御变化能力强,失效电流要足够高

- 透明性

透明性指的是在芯片正常工作时,用作ESD防护的半导体器件需要处于不工作状态,不能对芯片的正常工作产生干扰,而在ESD脉冲来临时,这些防护器件才能开启并工作。当ESD脉冲过后,这些器件又要能够及时关闭,否则也会影响芯片的正常工作,这要求这些防护器件要有比芯片的正常工作电压更高的维持电压,否则可能会引起闩锁效应导致芯片无法正常工作。

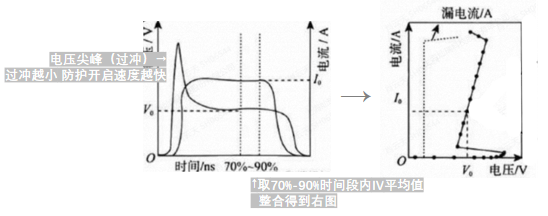

有效性指防护器件要能够很好的对芯片内部的核心电路起到保护作用,即当ESD脉冲到来时,防护器件要能够正常开启并工作,这在电学特性上体现为器件的

1.触发电压要低于芯片内部的击穿电压,并且开启的速度要足够快,这样才能及时地泄放ESD电流,保证芯片内部核心电路的安全,否则可能会出现核心电路已经损坏,而防护器件还没有开启的情况。

2.在开启后要有足够低的导通电阻,将电压钳位在比较低的水平,否则也有可能对核心电路产生破坏。

3.随着工艺制程的进步,核心电路中MOS管的栅氧厚度已经变得越来越薄,这要求防护器件的电压钳位能力也要很高

常见ESD防护器件

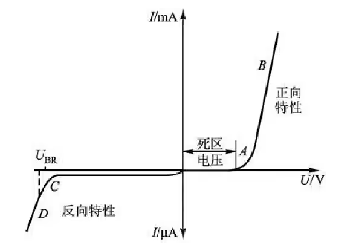

二极管

最常用结构,没有负阻区,通常与电源钳位单位搭配使用

优点:寄生效应少,正向导通电阻小,开启速度快。

缺点:正向二极管开启电压较低,导通电压约为0.7V,往往需要串联多个二极管,导致导通电阻和版图面积相应成倍增大,且高温下漏电流较大。

反向工作的二极管电流耐受能力较低。反向击穿后的二极管虽然开启电压较高,与PN结掺杂浓度有关,但其电流泄放能力很弱,导通电阻也较大。

N+/P-well型二极管常用于防护IO和VSS管脚之间的ESD事件(P-well通常要与VSS相连)

P+/N-well型二极管常用于IO和VDD之间

N-/P-well型二极管不常用

正向使用:死区电压时PN结未导通,超过死区电压后正向电流从uA增加到mA级别。

反向使用:在管子两端的电压大于一定值时,TVS管发生雪崩击穿,瞬间形成一个导通回路,将管子两端的大电流导出,并且将管子两段的电压钳制在一个固定电压,进而保护和它并联的电路

MOS管

优点:工艺兼容性好且结构简单

缺点:

触发电压过高。由于依靠NMOS漏衬结雪崩击穿来开启寄生三极管工作,在某些工艺下其雪崩击穿电压过高,可能导致内部电路先被击穿的情况。

导通电阻过高。由于GGNMOS通常需要较长的漏极到栅极距离来增强其鲁棒性,在泄放ESD电流时导通电阻过高。

单位面积鲁棒性较差。GGNMOS依靠寄生NPNBJT进行ESD电流泄放,相比二极管和可控桂而言,电流泄放能力较差。

PMOS用的少 空穴迁移率低 回执效应和it2都低

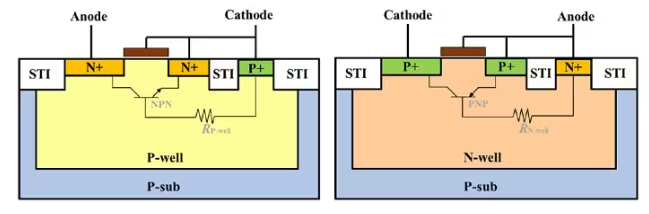

原理:寄生三极管

栅极接地的NMOS(GGNMOS)

栅接电源的PMOS(GDPMOS)

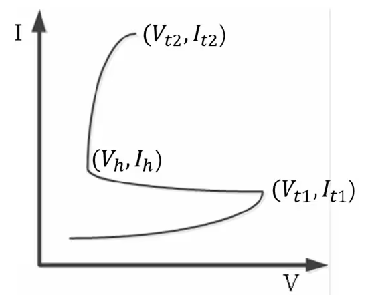

具有回滞特性(snap-back)

当ESD电压小于寄生三极管集电结的反向击穿电压时,NMOS处于关闭状态;

当ESD电压增大到超过反向击穿电压时,阱内将产生大量电子空穴对,电流流经阱电阻时形成负阻压降;

当压降超过三极管发射结的开启电压时,寄生三极管导通,形成低阻的电流泄放通路并出现snap-back特性。

当负向ESD脉冲施加在漏极上时,GGNMOS相当于一个正向二极管结构,同样具有泄放ESD电流的能力。

可控硅整流器SCR

最早是功率器件的一种。应用于ESD防护的SCR结构利用了集成电路工艺中的各种浓度的N型和P型阱以及注入区形成PNPN结构。SCR导通的正反馈属性决定了其更大的电流放大能力,开启后的深回滞特性也带来了更低的钳位电压。

主要优势:

SCR的电流泄放能力较强,远高于GGNMOS和三极管,单位面积鲁棒性强。

寄生电容较小。SCR的寄生电容主要来自于其多个PN结的结电容,相对GGNMOS电容更小。可以减小ESD器件寄生效应对高速、射频信号的影响。

SCR的深回滞特性,使得SCR箱位电压较低,同时由于SCR工作时的电导调制效应,SCR导通电阻较低

主要劣势:

触发电压过高。CMOS工艺上的SCR主要依靠反向PN结雪崩击穿来开启SCR,其雪崩电压很高(通常为P阱/N胖结反向击穿电压)。

回滞后的维持电压非常低,不符合ESD设计窗口电压下限要求,容易引起电路的栓锁效应。

开启速度慢。由于SCR雪崩击穿后,NPN和PNP BJT导通并形成正反馈所需时间较长,降低了SCR的开启速度。

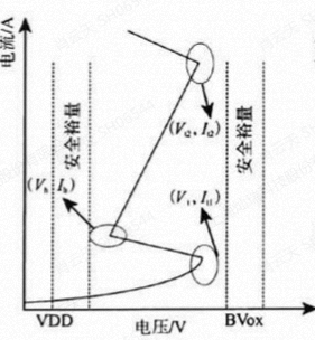

ESD设计窗口

使得ESD期间正常工作的区域

· 透明性:器件正常工作期间ESD器件不工作

开启电压(触发电压)Vt1>VDD

· 有效性:ESD时间发生时能钳住电压低于失效电压BVOX

开启电压(触发电压)Vt1VDD 并尽量提高

· 鲁棒性:超过泄放电流最大值后ESD器件会发生热击穿失效

击穿电流It2尽量提高

· 预留安全裕量:VDD~BVOX上下限各留10%~20%

ESD测试

- HBM和MM测试

- 1)IO和VDD/VSS:给IO施加正负电压,将VDD/VSS接地,其他管脚浮空

- 2)IO和IO:VDD&VSS浮空,给待测IO施加正负电压,其它IO接地

- 3)VDD和VSS:VSS接地,给VDD施加正负电压

- HBM和MM放电的持续时间较长,释放能量较大,因此通常会造成栅氧击穿、源漏穿通等现象。

- 通常要求为HBM2000V(10xMM),MM200V

- CDM测试

带电器件模型测试,由芯片自身存储的电荷发生转移所产生。模拟器件处理或组装过程中可能发生的静电放电,通常用于测试电子设备对静电放电的敏感性。

以P衬底为例,首先对芯片充电,连接与P型衬底相连的VSS引脚施加正负电压。充电完成后使其它管脚直接接地放电。

CDM模式放电持续的时间较短,产生电流的峰值很高,因此释放的能量会相对集中,通常会导致栅氧化层的针孔状击穿 。 - IEC测试

IEC 61000-4-2测试,使用电子枪进行接触放电测试,将电子枪口对准待测器件注入电流。

对于一些不能直接接触的系统使用空气放电的方法。

模拟设备暴露于静电放电环境下发生的放电,主要测试电子设备对静电放电的抗扰度。 - TLP测试技术

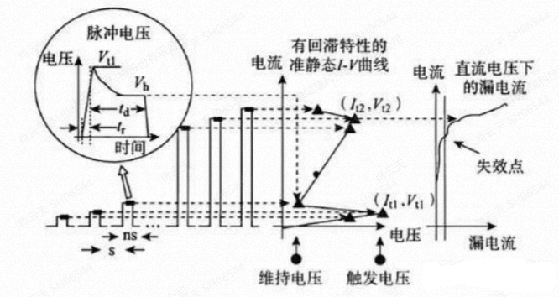

TLP——传输线脉冲发生器

传统的HBM、MM、CDM、IEC模型发出的是RC-LC模式的脉冲波形,直接的模拟了现实中的某种静电形式

传输线脉冲发生器发出的是离散的静电模拟方波信号,通过调节上升沿和脉冲宽度,间接地模拟了这些静电脉冲形式的损伤能力和不同上升沿CLAMP触发能力

组成:脉冲源、衰减器(减少反射)、测试仪器、测试器件(DUT)

脉冲源发出离散信号 模拟ESD冲击的瞬态特征

上升沿10ns 脉宽100ns 每个脉冲波形后测一次直流漏电流

漏电流在10^-10数量级为正常,

漏电流超过1uA或增大超过三个数量级则判断器件损坏停止测试