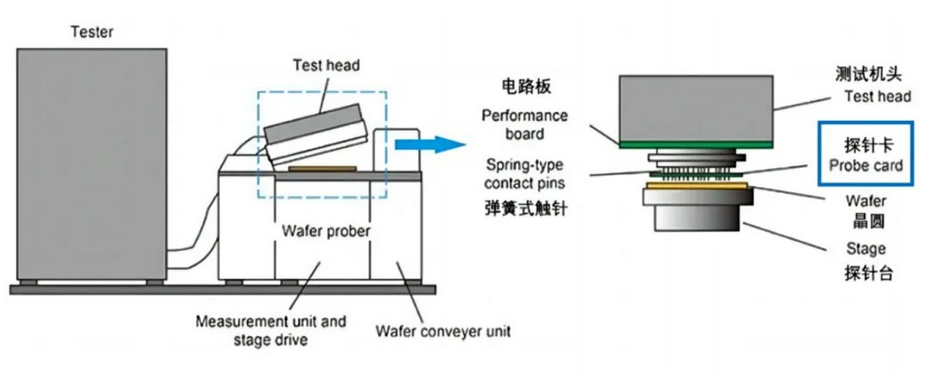

Pattern在芯片测试行业通常表示需要测试芯片的时序特征。在测试芯片的过程中,ATE机台会向被测试芯片的输入管脚发送一系列的时序,而在芯片的输出管脚比较输出时序,由此测试芯片是否满足其功能。狭义上可以将测试pattern理解为芯片的真值表。

与IC设计产生的时序不同,一般测试用的Pattern中的时序都是分割好周期的。而不同ATE公司之间的Pattern其语法是不一样的,由此也诞生了IC测试服务。一般来说各大ATE厂商都有自己的服务部门提供本公司机台的Conversion服务,但也有一些公司专门提供这方面的服务,即帮助各种客户解决不同ATE平台之间的Pattern和测试代码的转换。

Pattern内一般包含如下信息:Vector向量、Timing时序、level电平、Pin引脚

向量根据存储方式的不同,可以分为三种不同的时间/状态分配格式。

第一种是 TABULAR 格式,也是最常见的一种格式。其特征是一系列Vector码流,其中包含定义的所有引脚的时间信息和顺序排列的状态信息。横向为同一时间下各个引脚的状态,纵向为每个引脚在不同时间下的状态,随时间的增加从上到下依次运行。TABULAR 格式的示例如下:

1221 > 55,01,01,00,5f,73,00,00或

400.2 ns 0 0 1 Z 1 1 0 0 111 000第二种矢量格式是 SCRIPT 格式,其特征是单个 pin 状态和 timing 时间戳的组合。数据包含引脚名称,引脚当前的状态,以及引脚上从另一状态转换到当前状态的时间。运行时从上到下依据各个状态的时间戳切换对应引脚状态。 SCRIPT 格式的示例如下:

pin1 = 1;

time = 1044;

pin3 = 0;

time = 1121;

pin1 = 1;

time = 1239;

pin3 = 2;

time = 1505;Verilog VCD格式就属于这一类。

第三种矢量格式是 WAVE 格式,其特征是每个引脚的所有时间和状态信息单独分组。数据中先给出了第一个引脚的所有时间/状态信息,然后是第二个、第三个引脚,依此类推。 WAVE格式的示例如下:

Wfm pin1 @ons=0 @12ns=1 @124ns=0 @399ns=Z;

Wfm pin2 @0ns=1 @17ns=0 @113ns=1 @370ns=X;向量内的码值和定义如下:

| 码值 | 功能 | 信号方向 |

|---|---|---|

| 0 | 输出低电平 | 机台→芯片 |

| 1 | 输出高电平 | 机台→芯片 |

| P | 上升脉冲时钟 | 机台→芯片 |

| N | 下降脉冲时钟 | 机台→芯片 |

| Q | 保持上一状态 | 机台→芯片 |

| X | 高阻态 | 无输出 |

| · | 无操作(默认) | 无输出 |

| H | 采样比对高 | 芯片→机台 |

| L | 采样比对低 | 芯片→机台 |